计组17

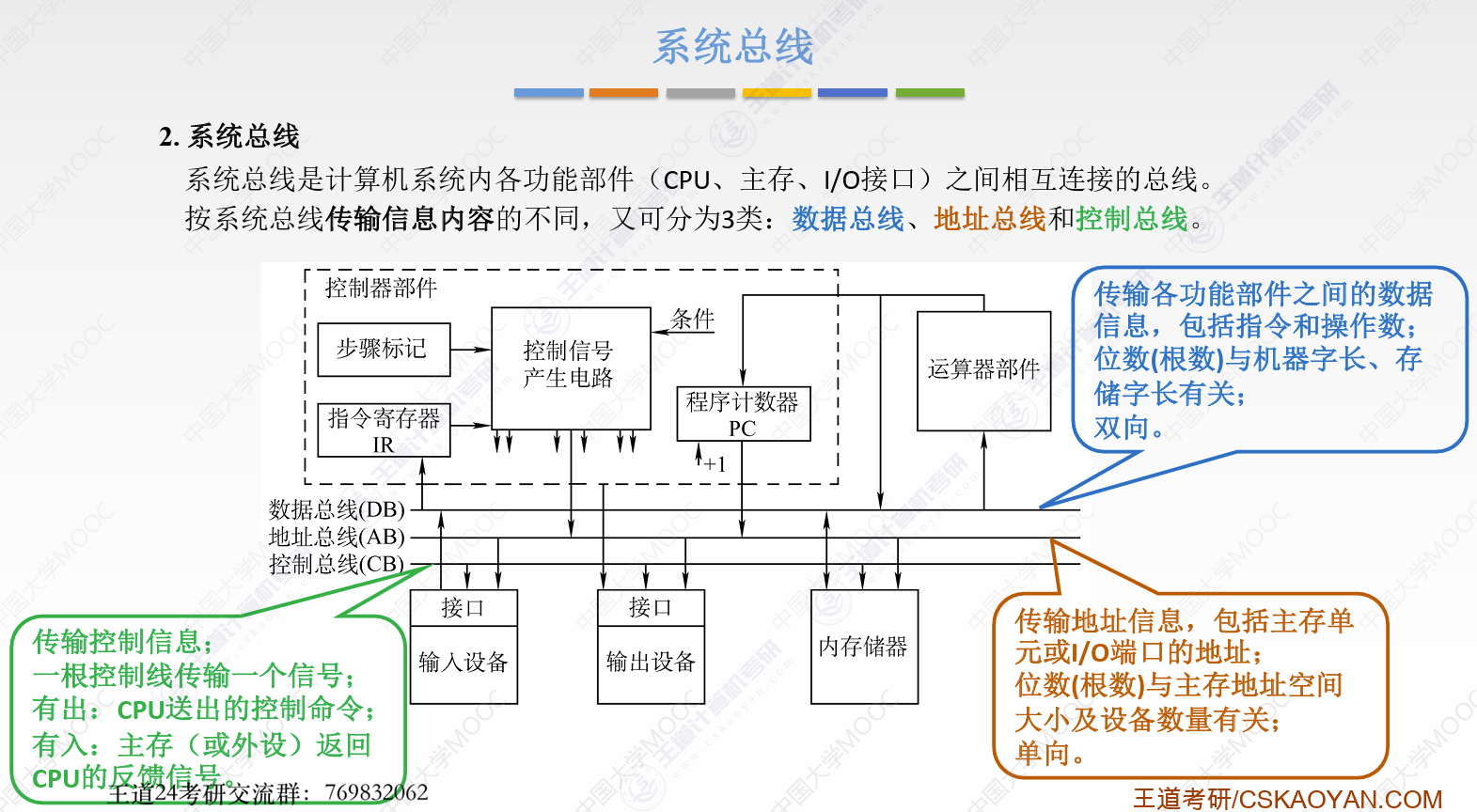

对于数据总线的一点补充:

数据总线的位数不一定和机器字长或者存储字长相同

如果机器字长32位,数据总线16位,那么CPU取得一个处理数据就要传两次

如果存储字长32位,数据总线16位,那么CPU得到一个存储字就需要访问两次主存

其他情况也是相对应的,类似于指令长度只有存储字长一半

地址总线,当外部I/O设备采用和主存统一编址的时候,那么地址也要考虑到

类似于主存有30个单元,但外面还有3个,那么至少就需要六位地址位才行,六根地址线

控制总线,对于单根线而言,是单向的,但是对于总线而言那么就是双向的

因为既有CPU向外部发出信号的线,也有外部向CPU反馈的信号线

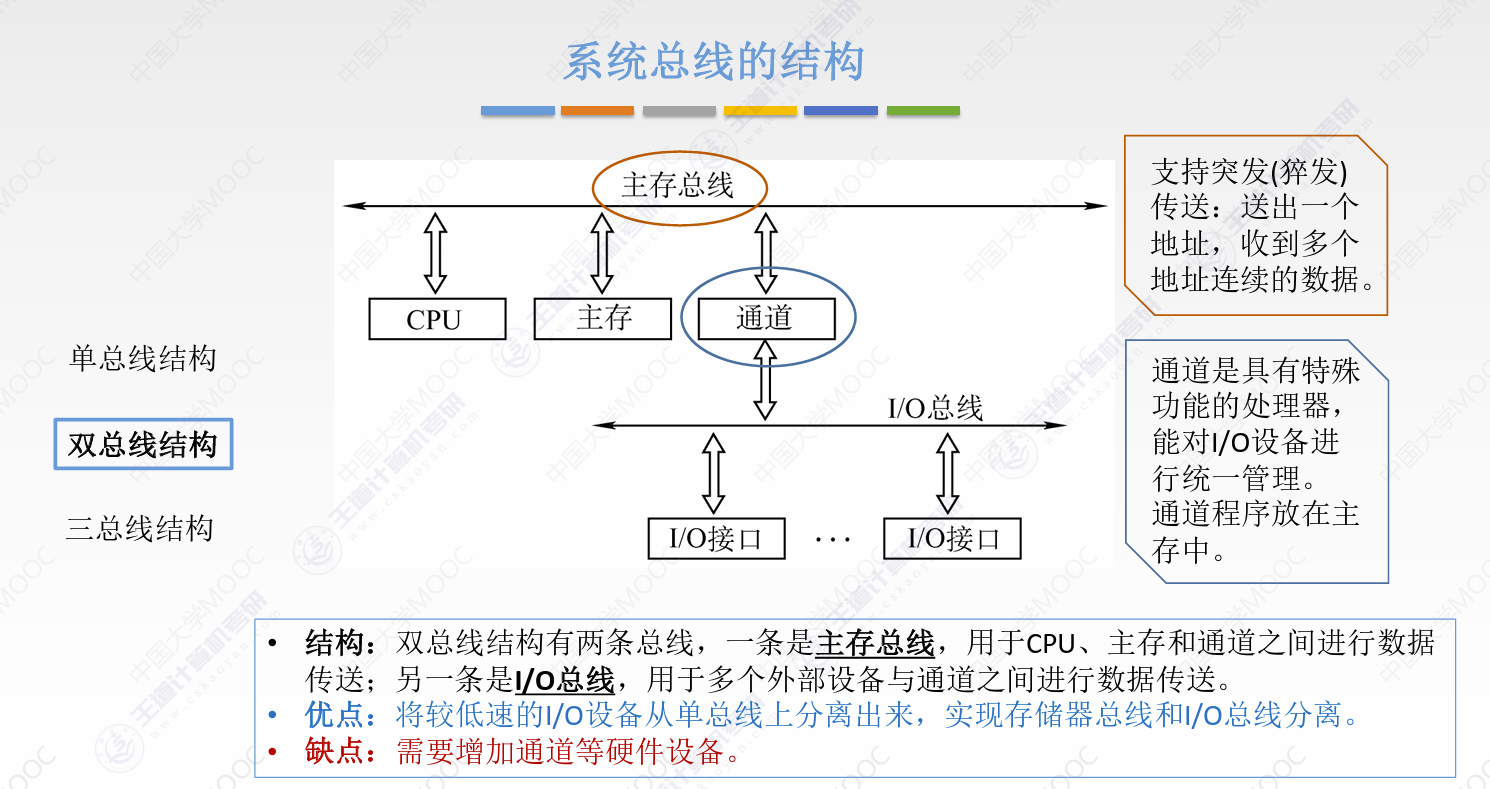

对双总线结构的一些补充:

存在的主存总线支持突发/猝发传送,即可以连续从主存中读取顺序数据而不必多次访存

很明显可以提高效率,减少访存次数

通道程序存放在主存中,需要调用的时候从主存中访问读取

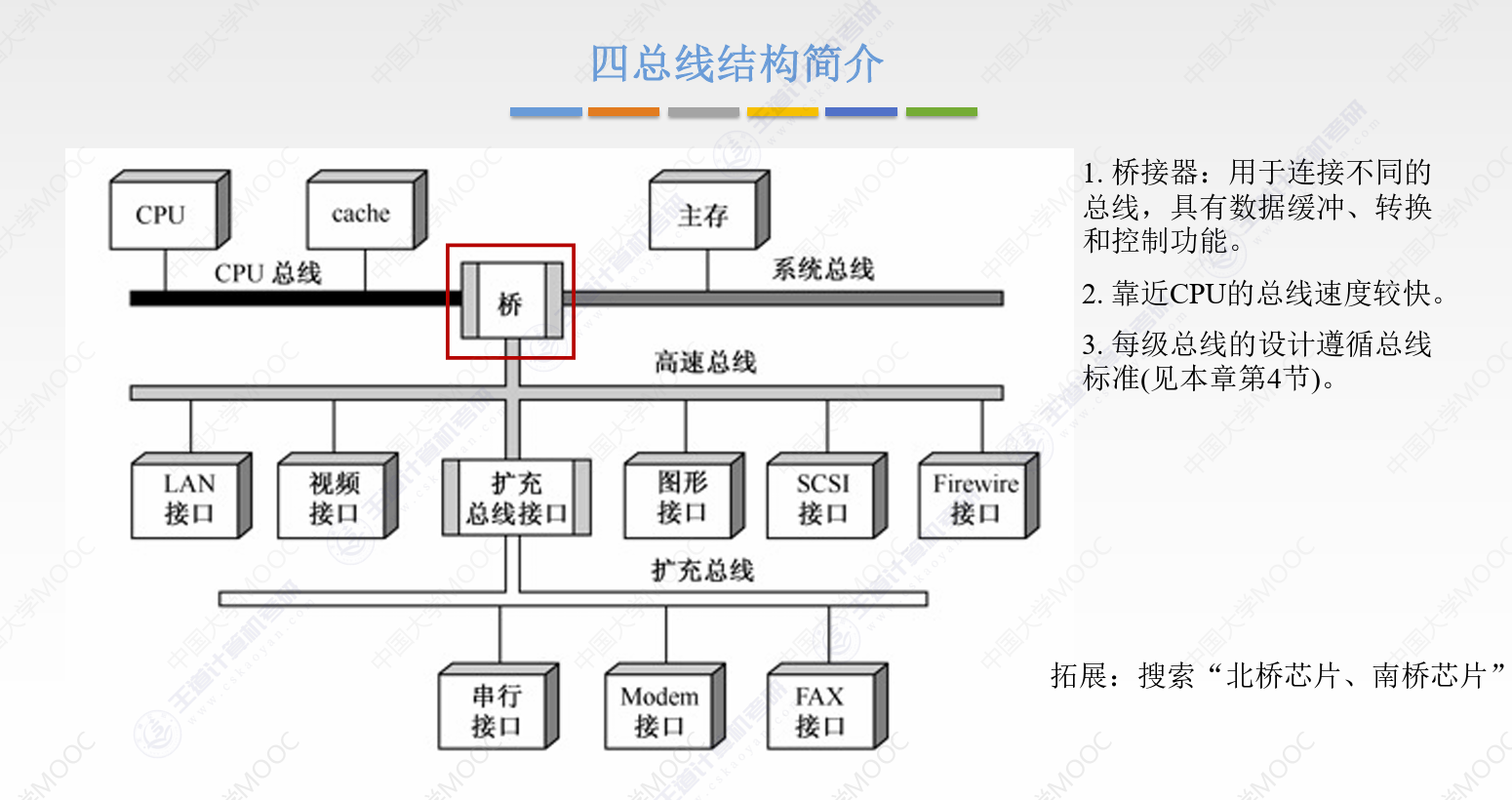

PPT上还有对于四总线结构的介绍,后续有空的时候可以看,但不是重点,是补充

这里对周期进行一个补充,一般来说总线周期是数个时钟周期

但也可能会有相同或者说倒反天罡,一个时钟周期包含多个总线周期的存在

上面是一些具体的计算概念

关于这道题,例题的一些讲解补充:

计算实际的有效数据传输位,因为往往传输时还会有一些校验位,冗余位的存在

所以实际的数据传输位并没有那么多的,要减去这一些无效数据位去计算

然后这边的发送首地址,并不是线复用时的特例,一般情况下也是需要先发送过去的

无非复用线的时候要注意潜在的数据、地址冲突情况

至于串行、并行两种情况的具体解释,其实王道书上面有

无非就是并行的频率不能无限制提升所以实际上限制了并行的数据传输带宽

本章内容多以选择题为主

其实一共也就那么几种总线时间协议关系

同步、异步、半同步、分离式

异步就是你需要传多久我就等你多久,直到你传给我了再说

拓展的异步串行是指异步时钟的,不依靠应答而依靠于校验码来判断传输结束与否

同步就是这个时间段你必须传好,不传好我也不管,直接开始下一个周期

拓展的同步串行就是发送方直接把收方的时钟控了让你强行和我产生一致性关系

然后通过校验码、开始结束标记传输

半同步就是约等于你传多久我等多久,无非我只会定时查看你传好没,而不是一直催着

普遍是在时钟上下沿查看一下

上面三种都是对总线独占式的,一旦占用那么总线只能等他们完成了再被别的使用

分离式的含义就是总线不能闲着,我只有传输的时候占用总线,传完了立刻就让给别人

这几种各有各的优缺点、适用条件,一般考察的就是这一些内容

异步里面的几个互锁关系:

不互锁:

A请求,B回答

A默认B会回答所以过一会儿撤销请求,B默认A得到了回答撤销请求所以过会儿撤销回答

半互锁:

A请求,B回答

A一定要亲眼看见B回答了才撤销请求,B默认A得到了回答撤销请求所以过会儿撤销回答

全互锁:

A请求,B回答

A一定要亲眼看到B回答了才撤销请求,B一定要知道A已经得到回答撤销请求再撤销回答

稍微比较绕吧,但应该还是能理解的,建议看书

另外就是总线的几个阶段

突发、非突发两个方式要清楚,经常考

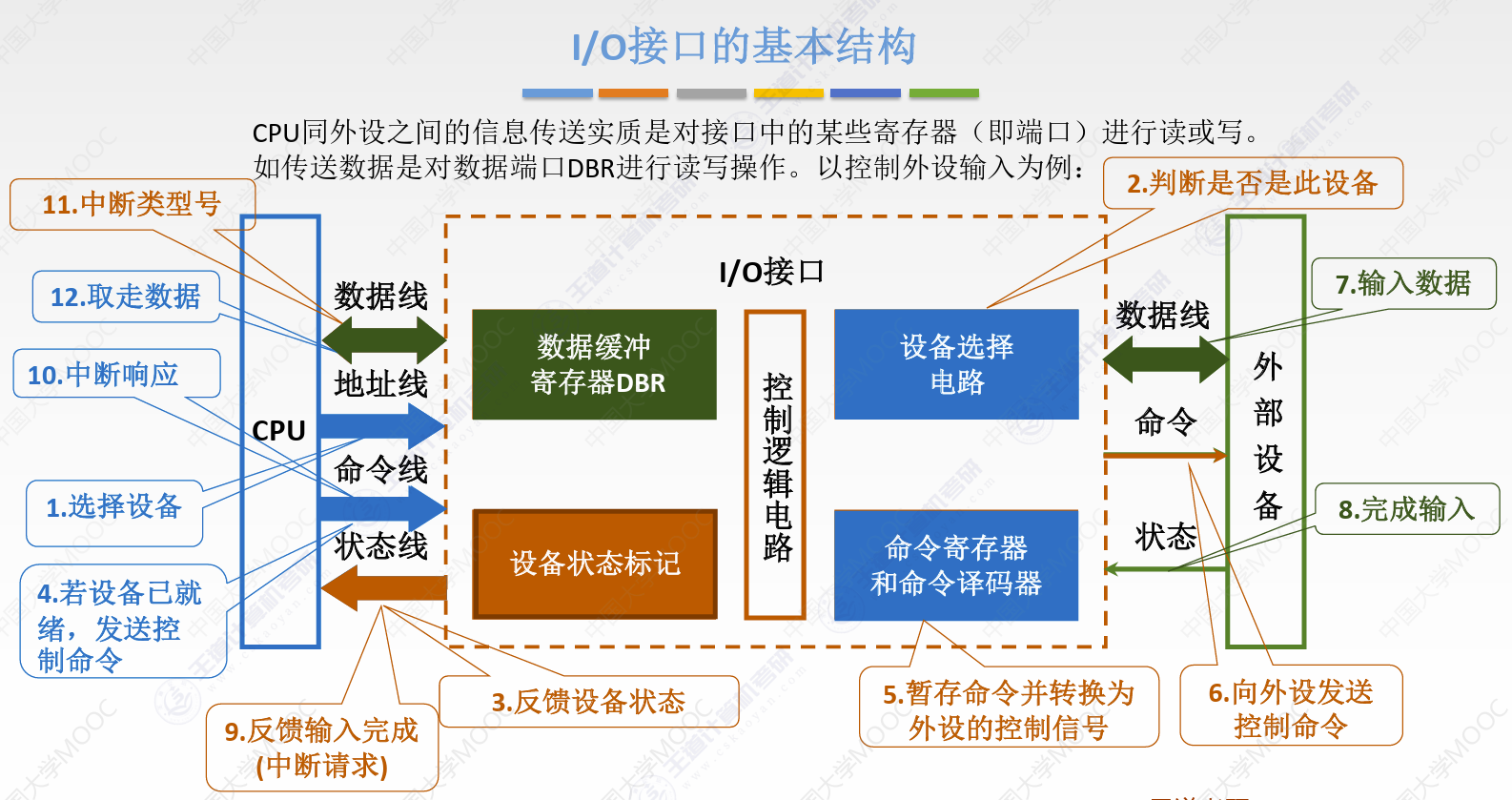

I/O接口的功能:

书上也有详细介绍,这里不过多赘述,基本要求是能背下来,或者是都知道

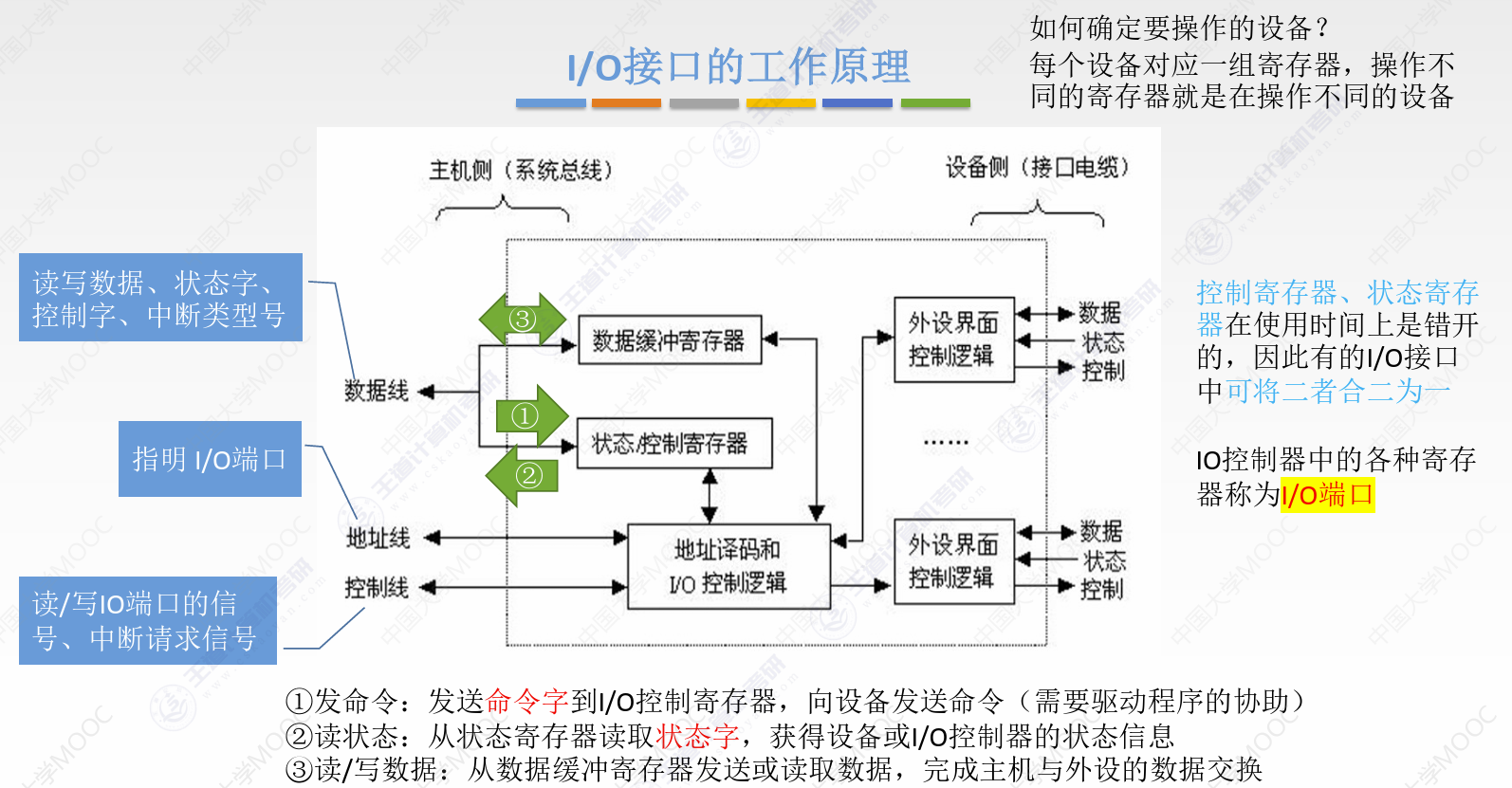

对I/O端口的一些补充:

对于书上7.1图中的内容,补充一点:主机侧并不一定是并行传输接口

不过I/O接口的串/并转换功能自然还是需要有的,否则外面一个并行的不就寄了?

至于状态寄存器、控制寄存器书上一句话的理解:

其实是从其工作流程出发,CPU向I/O接口发出一个命令字到控制寄存器里面

然后控制寄存器的内容给译码器,之后这个控制寄存器实际上就已经不需要再用了

因为已经选中了相应的外部设备,这个寄存器就可以在外部连通后用作状态寄存

即,在1阶段当作控制寄存器用,在2阶段都当作一个状态寄存器用,完全不会产生冲突

注,这里的控制线基本只有没几个命令,大多数命令都是在数据线上完成传输的

控制线基本只会传输一个读写信号、中断、仲裁、握手,大部分都会是数据线上面传输

例如一个指令字,其就是在数据线上传输而非在控制线上传输

书上对于传输内容写的比较浅,这里可以用作补充,包含了各功能部件、各工作流程

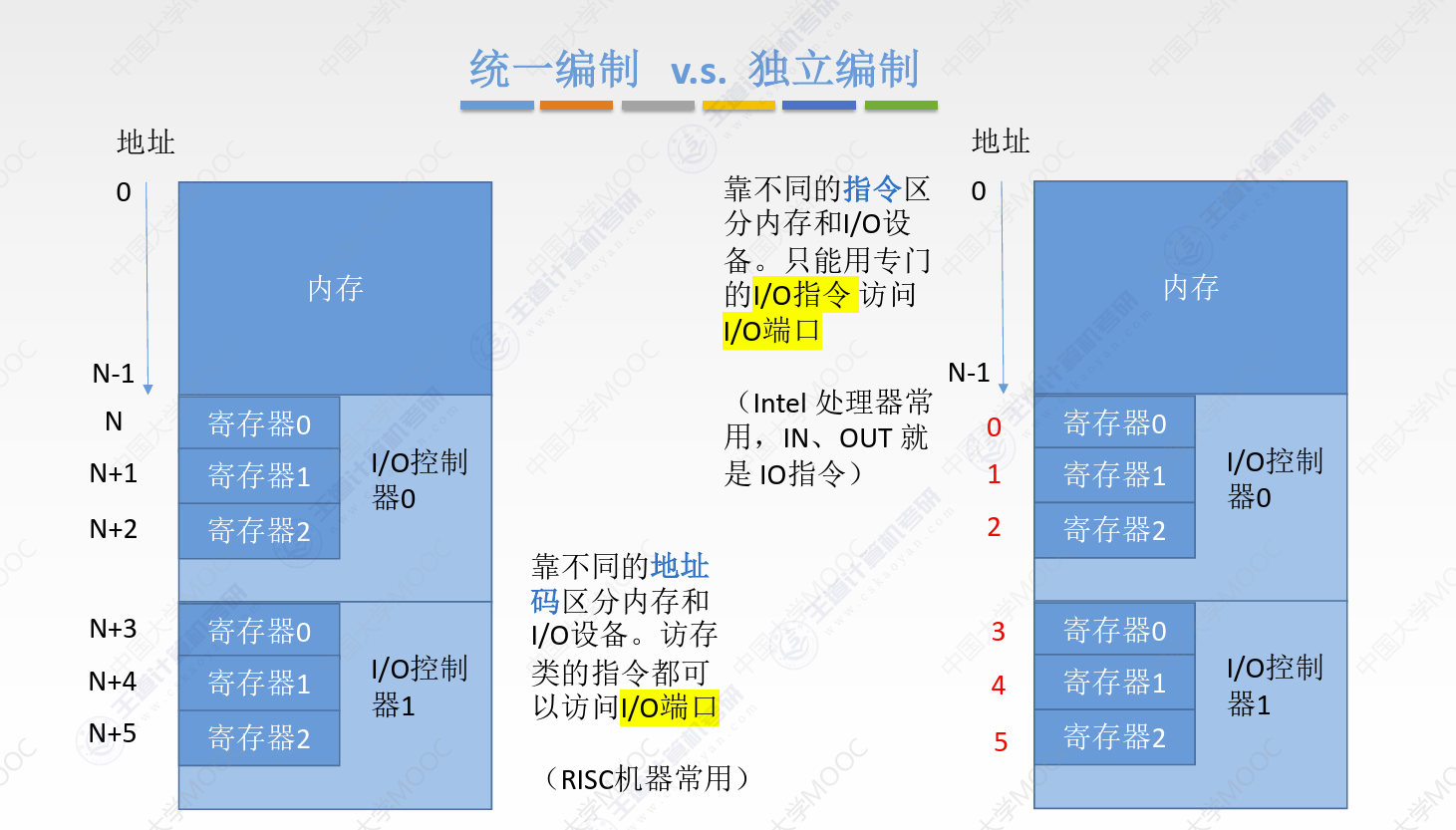

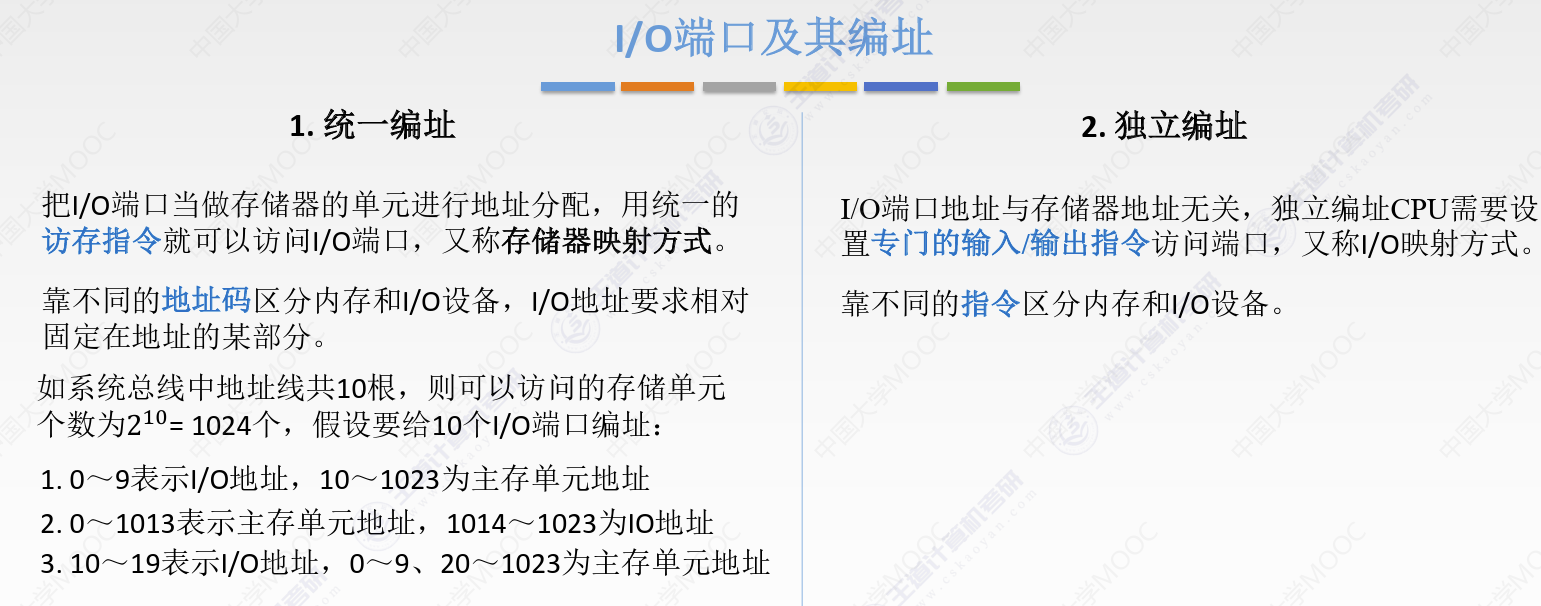

关于编址方式的较为形象的理解:

后面的计算还是比较常见的考察方式,其他的细节还是要看书的,还有不少内容