计组14

第一节的内容是一个介绍,略微啃下即可

先谈硬布线下的指令、机器周期、微命令、微操作的关系:

一条机器指令可以被解释为多个机器周期,如取指、间址、执行、中断指令

一个机器指令一般包含这四个周期

每个机器周期内部可以包括多个微操作,每条微操作都会对应一条微命令

例如取址周期内,需要完成PC->MAR,M(MAR)-MDR,(MDR)-IR,PC+1-PC

这些需要完成的步骤,每一条都可以被称为微操作

而令这些操作能够对应完成的命令,就称为微命令,如对PC-MAR,需要PCout,MARin有效

这样一条命令就是对应一条微操作的,整体视作是一个命令

而每个机器周期往往有多个节拍,能够相容在一个节拍内的就称为相容微操作

这个节拍即为一个时钟周期

硬布局下没有微指令这样一个说法

然后再来谈下面的内容:

CPU判断当前应该发出哪些信号,是根据各组输入信号的组合来判断的

操作码、节拍、当下的系统状态标识、指令周期是四个判断的维度和标准

因而为了确定当前应该发出哪些信号,实际上需要一个组合逻辑表

当A怎么样,B怎么样,C怎么样,D怎么样…的时候该输出什么相应的信号,硬布线

硬布线解决的就是从硬件上直接根据电路设计来完成这件事

考试对其的考察并不会特别深,毕竟这是计算机组成原理而不是硬件布局

但是最基础的做法还是要知道的

首先就是输出问题,当确定某种情况的输出后,某个端口输出一个信号,即一个微命令

把这几个相关的操作控制器均连在这条线上即可

例如C1高电平的时候需要完成PCout,MARin,那么把PCout和MARin的控制器和C1相连即可

然后再来说较为复杂的输入确定输出组合逻辑问题:

首先先说不同指令模式情况下的法则,一个是定机器周期指令,一个是不定机器周期指令

定长周期指代机器周期的执行时间均设置为一个机器指令中最长的机器周期执行时间

不定长就是上面的反话,你需要几个执行时间就给你几个执行时间,一般以时钟周期单位

至于做法,这里单独放在末尾

重心还是放在后面微指令为主

还是先来解释下几个之间的关系,微程序、微指令、微命令、微操作

这里就是把上面所说的每个机器指令(如取址、间址)给封装为了一个微程序

每个微指令都会成块放在里面,然后对应的微操作也会顺序放在块里面

一般不仅仅包含公用的这一些,还有更多的如运算等,也就是出厂就全部写好了

任何情况下应该干什么全部都被记录在里面

这个机器周期需要完成的事情,也就是其中蕴含的微指令就这样被包含在了微程序里面

同样的,每一条微指令对应可能有多个微命令,每个微命令又对应一个微操作

本质原理是一样的,就是什么时候应该干什么,不过把硬布局给改为了存储器内存储

当某些信号给过来的时候根据这个信号去控制存储器里面找到相应的微程序,然后去执行

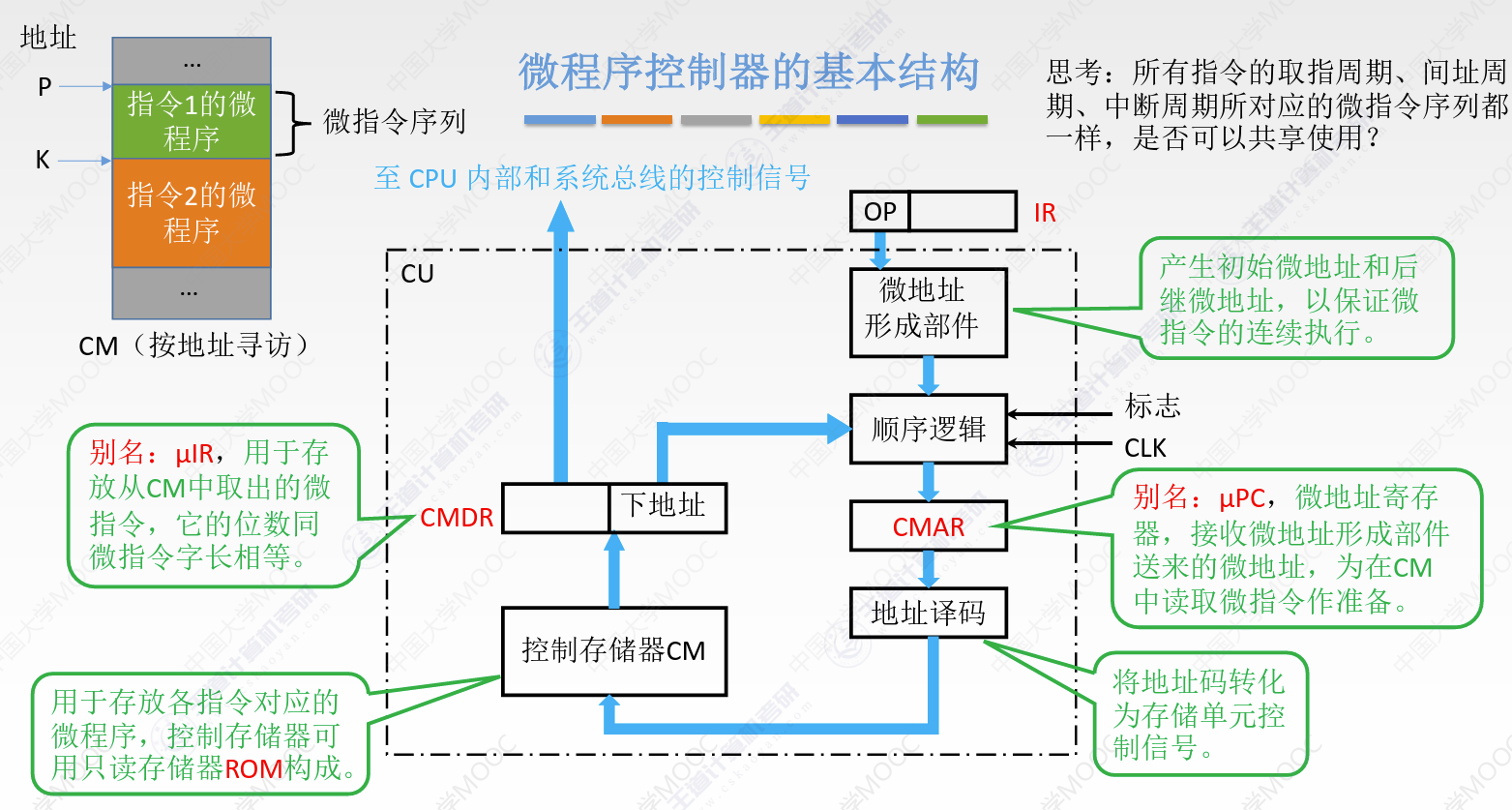

然后再说这个微程序控制器的基本结构问题:

首先CM是采用ROM的,因为断电后不能丢失指令

然后描述下其的工作流程和组成:

从指令寄存器中读取到一个操作码后,就要去相对应形成一个微程序地址

因为都是按照微程序地址存放的,给定一个操作码我就一定要去明确这个微程序从哪开始

所以才需要这个微地址形成部件的存在

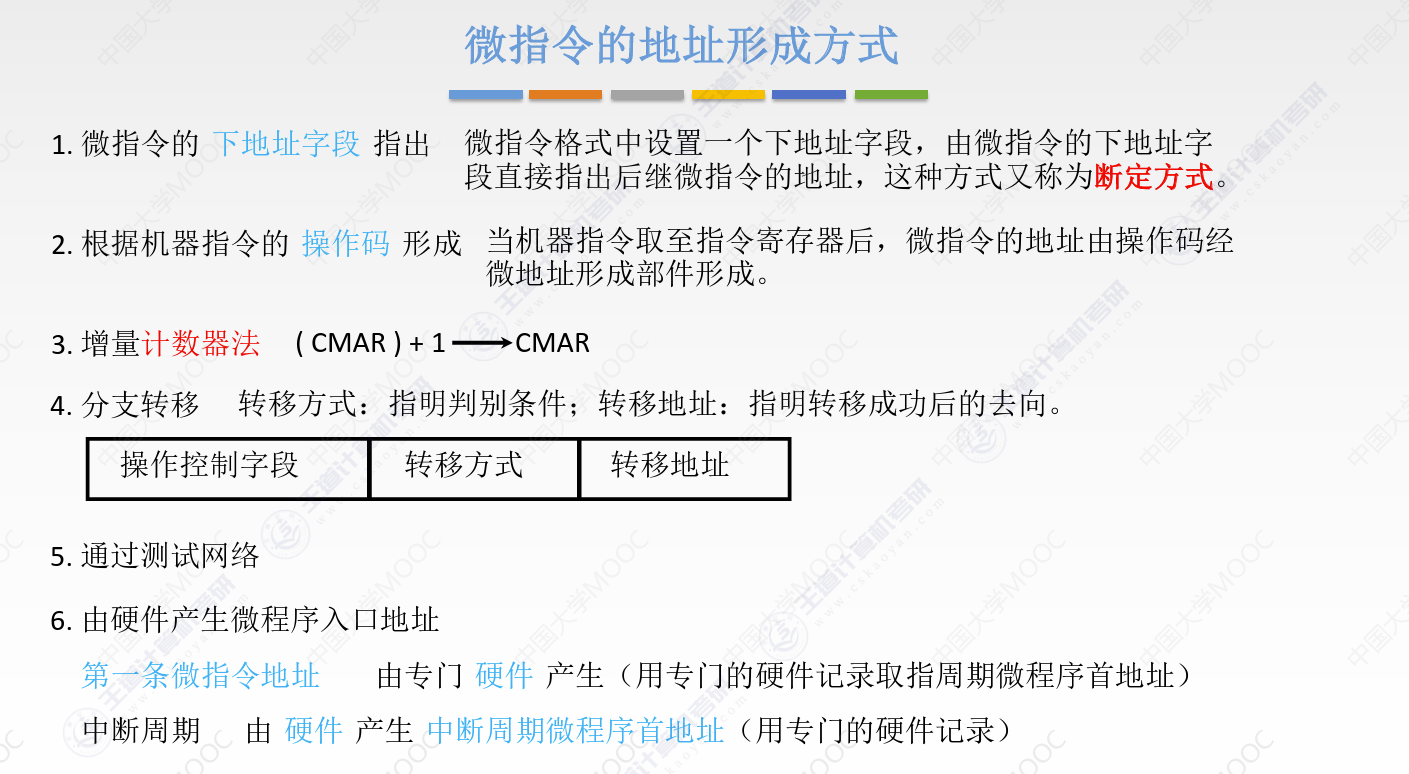

然后因为不一定是顺序访问每一条微指令的,可能会有跳转,所以才需要顺序逻辑器

根据一系列外界信息决定到底执行哪一条微指令,并把地址放在CMAR中,经译码器选单元

将该微指令取出后存放到CMDR中,需要注意的是,每一条微指令都包含两个结构

一个是操作控制字段,即是给总线、外部的控制信号

一个是给内部的进行下一轮执行的顺序控制字段也称为下地址

将这个地址给顺序控制逻辑器,然后再根据一系列外部信号来判断到底执行哪个指令

相对应的给出对应的存储单元地址

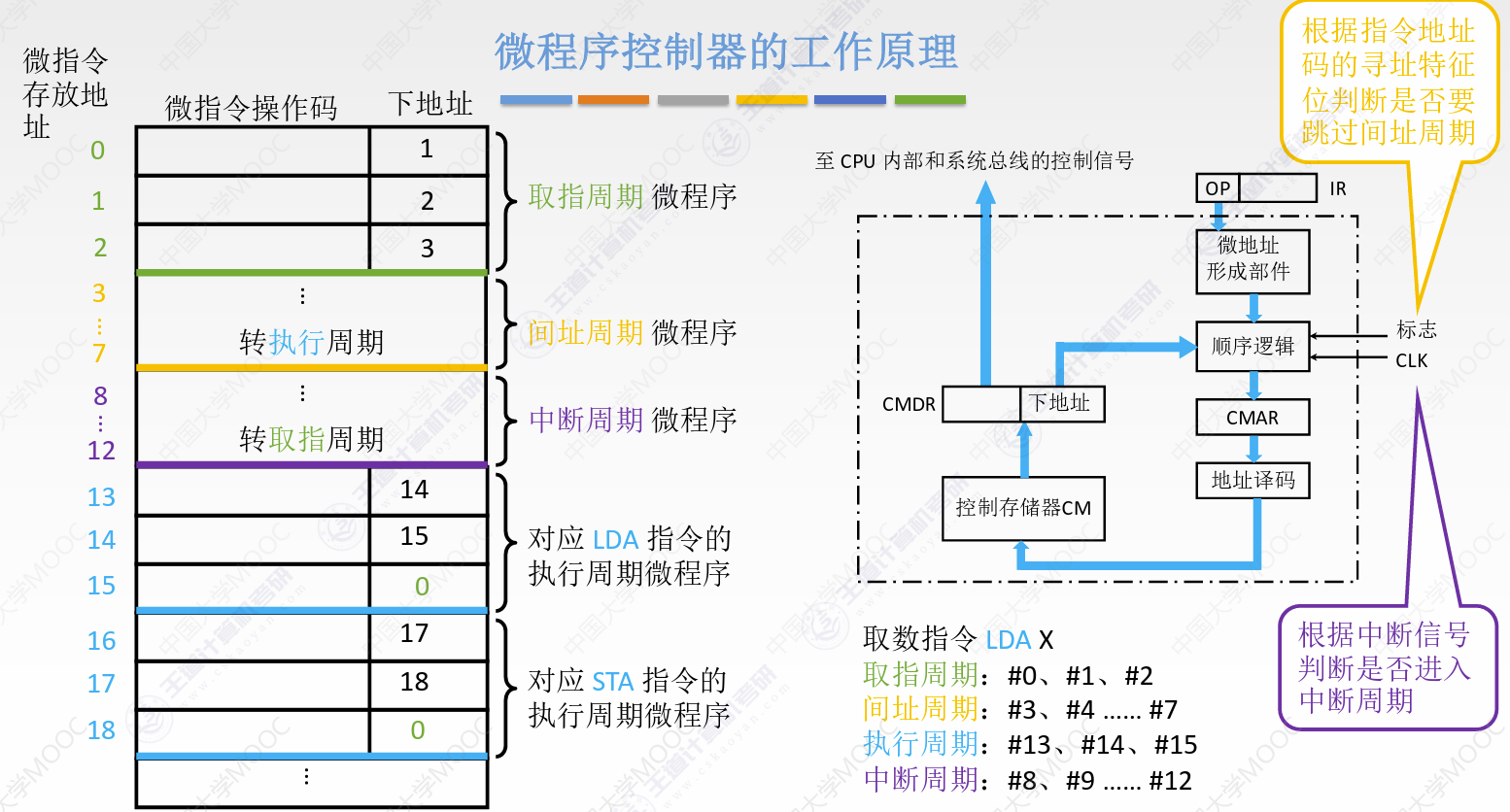

因为每条机器指令都包含四个公共的周期即中断、间址、取址,所以是可以放控制存储里

一般都只有单独的一份,毕竟没有必要有两份

只有执行周期的指令是不固定的可能有很多很多类型

对于标志位、CLK,其实就是对中断、间址的判断逻辑,看IR的地址码段给的信息位决定

后面到底应该是继续执行下去,还是说跳转到别的微程序块执行

另外就是一个考点:

如果某指令系统中有n条机器指令,则CM中微程序的个数至少是n+1个

因为至少有一个取址周期的公用段,另外两个不一定有,没必要追究为什么

同时有的选择内把取指周期和执行混在一起当作一个

指令周期!=微指令周期

然后就是微指令的格式问题:

其实也很好理解,水平型就是一条微指令包括多个微命令,垂直就是只包含一个

其最基本的格式是需要清楚的,至于混合型没必要深究

然后再说不同的编码方式:

一种是直接编码,即每位表示一种操作,如果选中这个操作其他都需要置零,以位表示

一种是字段直接编码方式

将控制字段分为多段,且每段可以以数值表达而非用位表达,7位就可以128种类型

考察而言无非就是给定段的长度考可以多少种,以及给定种数判断需要多少位

尤其注意下一个000或者0000不执行操作的情况,也就是需要留出一种操作判断的情况

这个常考

字段间接编址,书上写的也很简单,不太重要

然后再说地址形成方式,指的就是之前的顺序控制器的地址形成法,细化了一下:

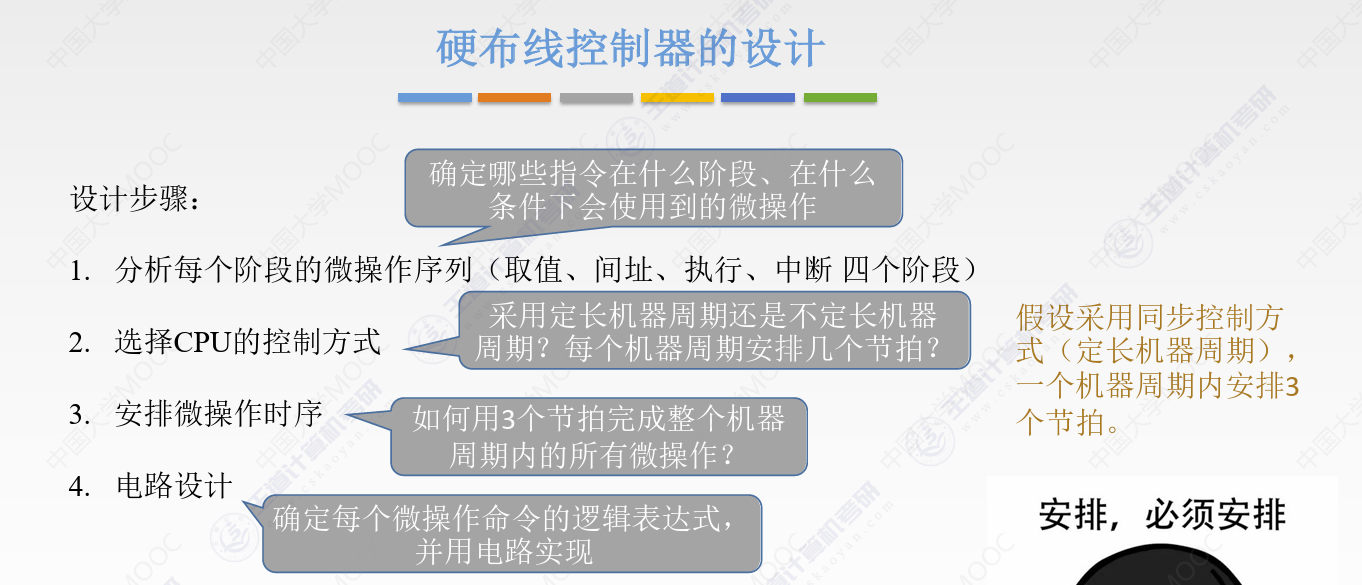

硬布线设计以及控制单元设计:

首先就是写出每一个微操作序列,每一个周期的操作序列,然后再看是否定长周期

定长周期就是以最长的不会产生冲突的一个微序列为一个周期

一般一个节拍内可以有多个微操作,但访主存例外,只能单独扔一个时钟周期

于是所有的周期,都是以这个最长周期为周期了,也就是确实会有浪费存在

不定长那么就是怎么短怎么来,与上面比较相差的无非就是几个空余的时钟周期罢了

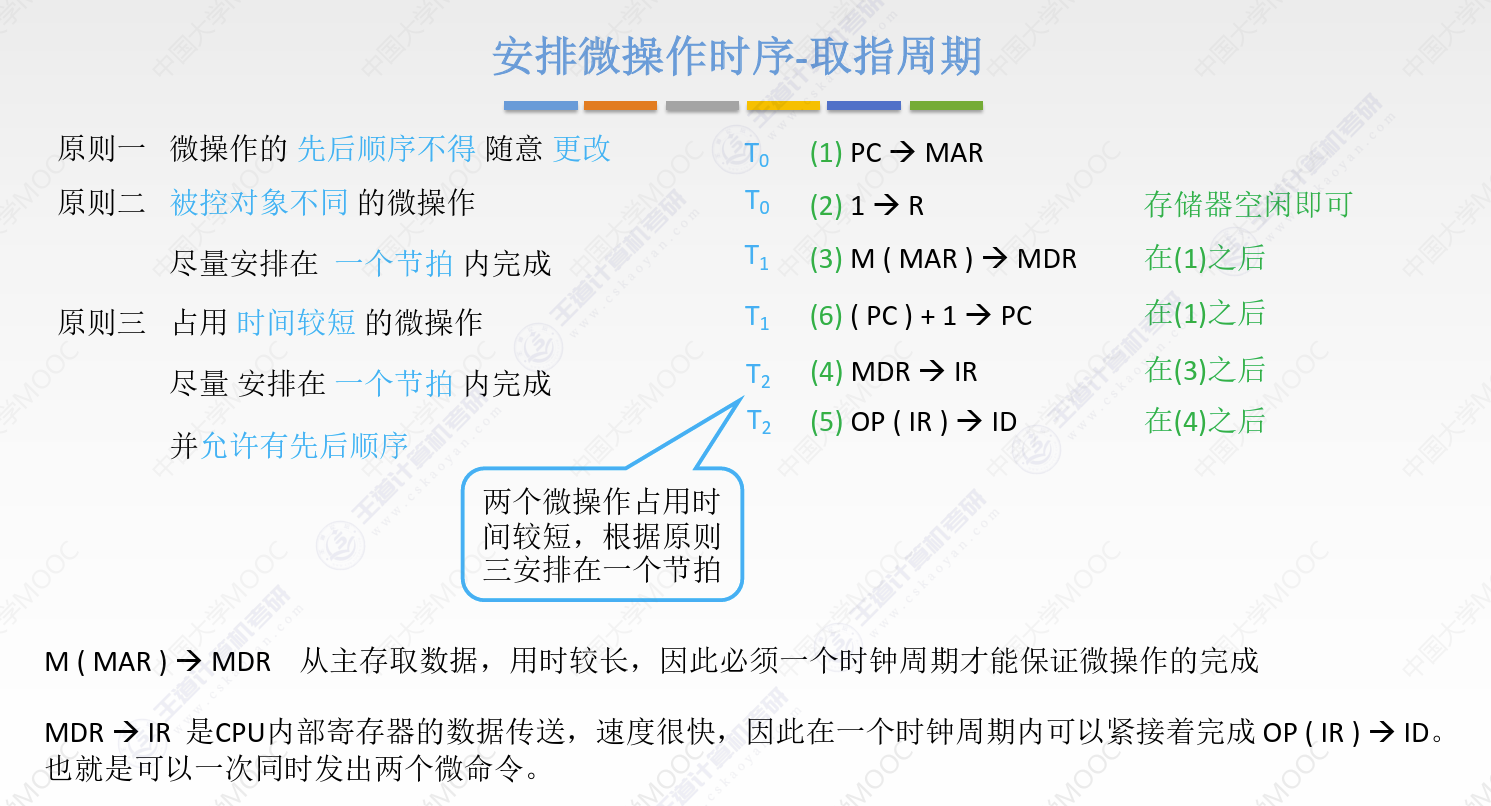

然后就是最重要的时序安排:

在写出每个微操作序列以后,要确定每一条微操作的前后逻辑关系,谁必须在谁后面的

以此去安排最基本的时序周期

先拿取指周期作例子:

首先是需要先给主存一个读的信号以后,才能去根据地址读取,所以分配在不同时钟周期

再是访存操作,其是必须要耗费一个时钟周期的,相应的寄存器也只能一个周期后才访问

所以把MDR的读取放在了下一个时钟周期,而内部寄存器的传输完全可以安排在一个内

这里需要注意的就是有微指令后,需要把送到ID中去(指令译码器

另外就是间址、中断,基本都类似,步骤和流程都是类似的:

先确定先后顺序,然后再根据先后顺序、是否互斥安排在同一或者不同时钟周期

再看能否精简,能精简的则进一步合并

最终会得到一些组合逻辑表,其实就是某条指令在某周期什么状态下会执行

把这些组合逻辑表中该指令的相应执行条件给全部加起来,再以离散数学方法合并为最简

然后以此设计电路:一般不会考那么难,顶多就是两三个序列一条指令,不必画表

其实一般而言设计出微指令的微操作序列,分配好时钟周期后即确定一条的执行条件

然后再说微程序控制单元的设计:

设计相应的时钟周期序列是和硬布线没有区别的,都是按照几个步骤去设计序列

这里有区别的就是需要添加几个微指令特有的操作

每一个时钟周期结束后都需要确定下一条微指令的地址,一般就是一个周期一个微指令

这里当然说的是定长机器周期的状况

每一个机器周期结束,也就是每一个微程序结束后都需要确定下一个微程序的首地址

具体是对微指令执行过程的细化

总体肯定是以博客、PPT内容为主,书上的就作为进一步细化理解补充用的

具体的复习建议:

第一节的内容是一个概括性介绍,可以粗看,大致上略过为主

第二节的硬布线,首先清楚硬布线的原理,即:什么时候什么情况什么条件应该干什么

衍生出硬布线的电路设计,电路设计往往不是重点,但安排节拍的操作往往是重点

对应节拍安排,建议一定要把握、理解并且能够清楚各个命令执行的逻辑关系和细节问题

尤其是逻辑关系以及一些细节,这块把握不够的

然后就是硬布线相应的一些优点、缺点、适用性、特征等

书上写的还是比较详细的,可以配合王道的知识点、博客的知识点进行回顾补充

第三节的微指令,最核心的就是清楚其整个结构和工作流程,后面的也会进一步细化

然后就是知识点、概念性的事情,第一个就是记住其英文名词

例如往往把几个通用的机器周期给放在这个CM中,CM往往用ROM设计

指令、机器周期、微程序、微指令、微操作、微命令之间的一系列关系

以周期结尾的各种周期之间的关系

然后再是微指令的设计,这一块建议配合博客、书、PPT的思维导图一并复习

这里是会有一些计算相关的问题,稍微注意下这一块,课后习题也有

最后就是微指令控制单元的设计,最后两个的确定格式、编写码点个人并没有细化了解

注:

还是建议平时偶尔刷一次这些博客,并不是单纯的记录,更是一个补充性的