计组5

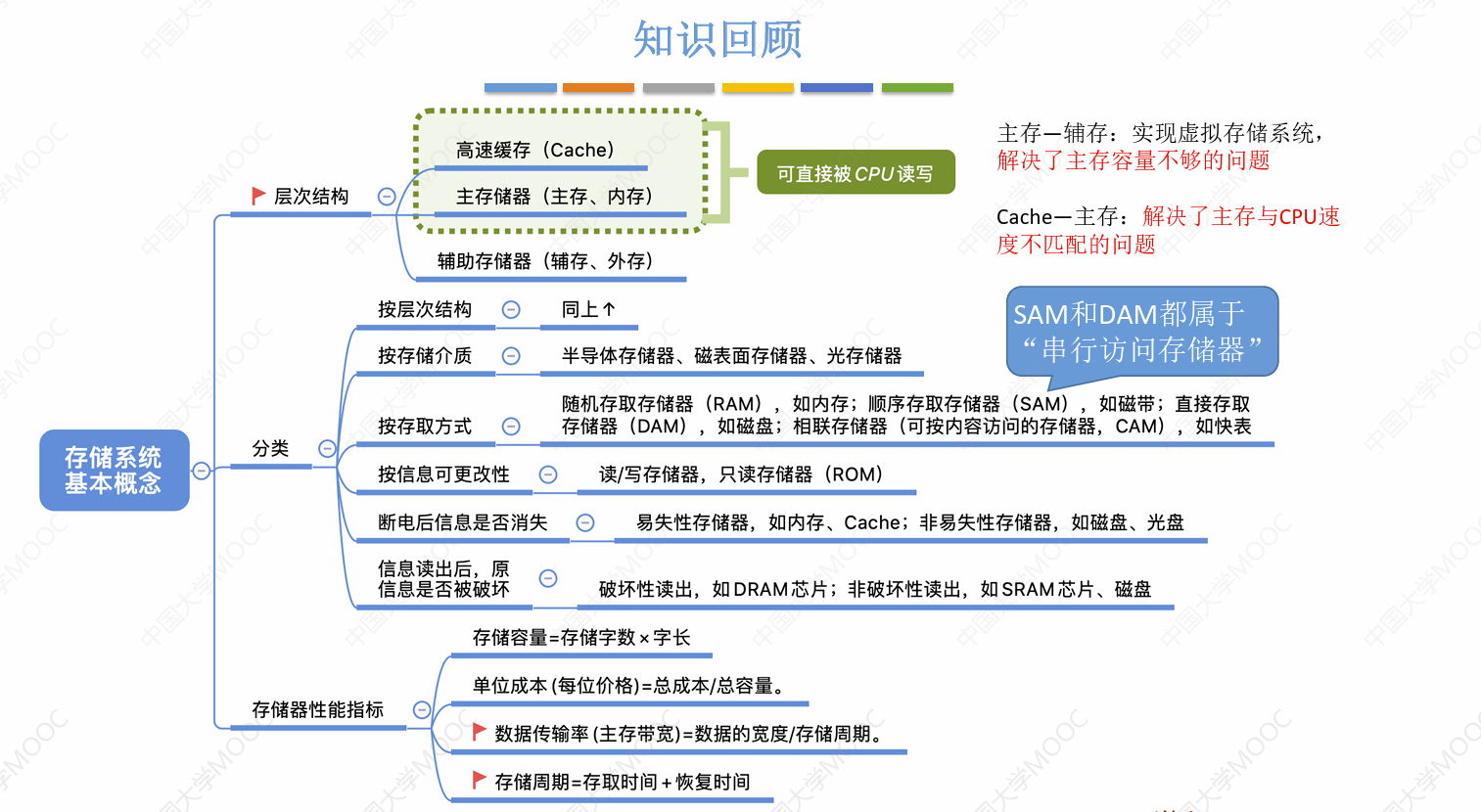

略微关注下其中的存储器分类,尤其是除存储介质的后面几个,书上都有,多去看

都是偏概念的东西,常见的东西、英文名出来需要知道它是属于哪个类别的,到时候整理

补充下层次结构,书上基本都有,不多赘述

注意下层次结构里面最高还有一个寄存器的存在,别忘了这个在CPU内存在

关于命中率,先从cache里面找,再去内存里面,再去外存里面

这是一个概率问题,越是上层的内容存储的越是经常被调用的东西,下层的访问概率很低

所以容量越来越小、速度越来越快、上面的命中率也会非常高

寄存器、Cache、主存都可以直接被CPU访问,相关的操作由硬件还是软件结合见上图

另外,CPU的速度是远远快于存储器的存取周期的

关于寻址:

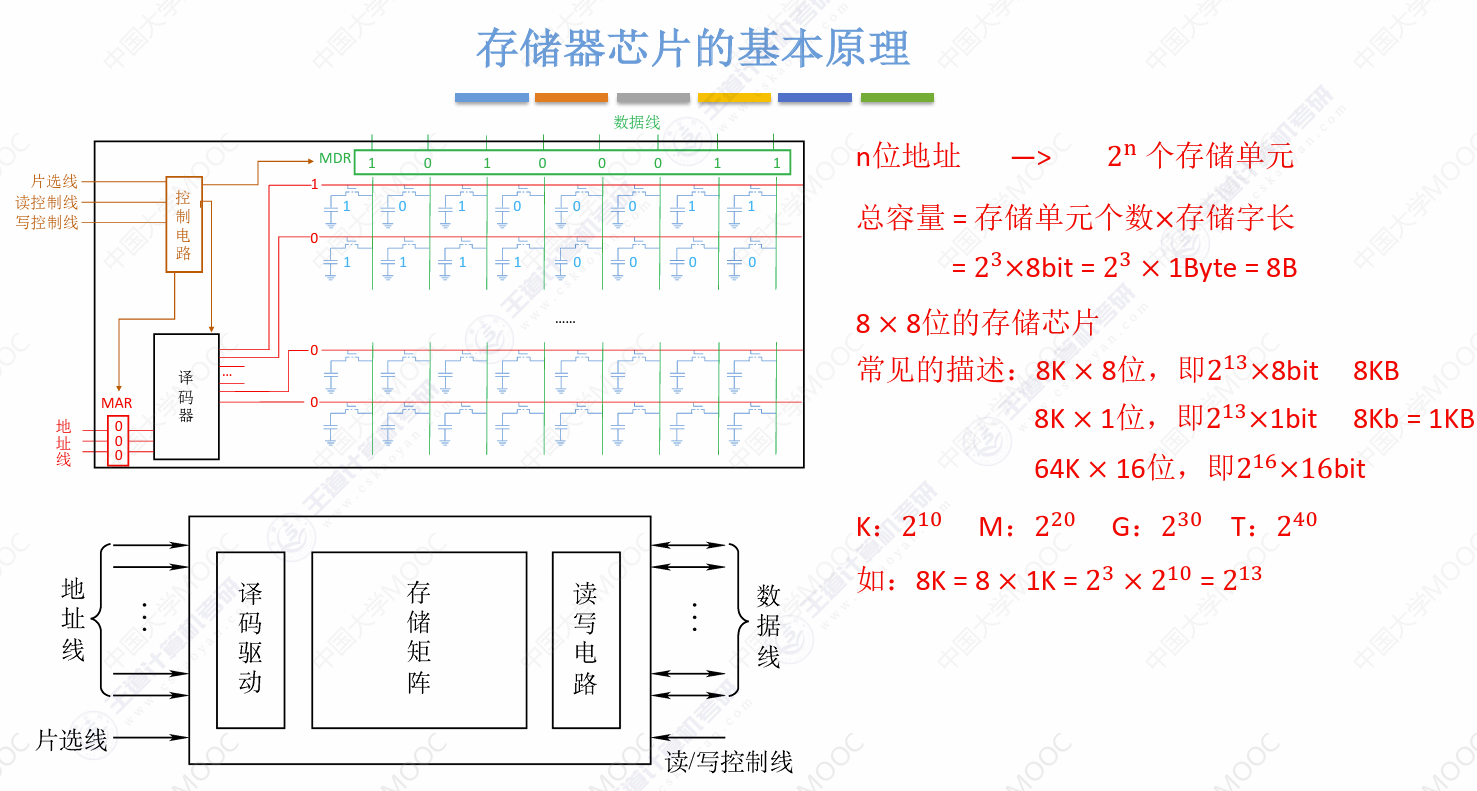

一般可以这样理解,按字节编址,意思就是把多位存储元视作一个存储单元

即,给一个存储单元一个地址,这个地址实际上也就分配了该存储单元所占用的存储元

一个字节就是8位/8个存储元视作一个存储单元,这里当然是默认存储元是一位二进制的

图内谈论的实际上是存储单元矩阵,将多个8位的存储单元视作一个单元,本质一样

例如按字节寻址那么每个单元就是8位

简单理解就是存取时间其实比较短,但是因为后续需要恢复,所以周期比较长,冷却时间

存储容量这边,实际上是存储单元的个数乘每个单元存了几位得到的内存

其中这个位,一般而言MDR的位数就是这个位数,引脚数、数据通路数也是这个数

MDR的大小不一定和存储字长一样,因为数据带宽也不一定一样,每次或能取好几个单元

例如,以字节编码,那么就是8位一个单元,字长编码,那么32位机器就是32位一个单元

存储速度的计算那边,需要注意单位转换,这边历来是考察重点,书上题目多看

关于SRAM/DRAM的差别,首先RAM是随机读取存储器的简称,S是静态,D是动态,英文

静态采用的是稳态电路,只要不断电那么电荷就不会出现漏出的情况,所以不必刷新的

而动态采用的是单晶体管,所以会产生漏电荷的事情,所以就需要刷新来解决

一方面是每次读写,都会破坏这个晶体管电容的电荷量,所以每次读写都需要对单个刷新

读、写两种操作都会导致电荷量的变化,就需要去单个行重写一次,读后刷新

一方面是一段时间内电容也会漏电出去,所以必须间隔一段时间全部刷新一次

一般默认为2ms,单位运算

因而自然引出三类不同的刷新策略

都是字面意思

另外就是主存而言,其的存储量一般是比较大的,所以如果采用非行列存储,引脚非常多

但即使采用了行列存储,地址位也仍然很多,所以需要采用引脚复用,Cache就没这种烦恼

即,先写入行信号,再写入列信号,中间会有延迟,这边还有一点小细节

需要在行选中信号前把行信号给输入到引脚,同样也需要把列选中信号前把列信号给引脚

在行信号选入后,需要保持这个行选中信号直到使用以后为止

而列选择信号是在行选择信号之后再输入的,在列选择信号之前需要给定读写信号

在列选择信号也进入后,那么三个信号就齐全了:行、列、读写,就可以用了

不过不怎么考,佛系即可

Cache因为存量并不大,所以没必要采用复用引脚,本身就没几个引脚,一次性给定的

SRAM本身就是静态,含义即为非破坏性读出,读出后自然不需要重写,不用刷新

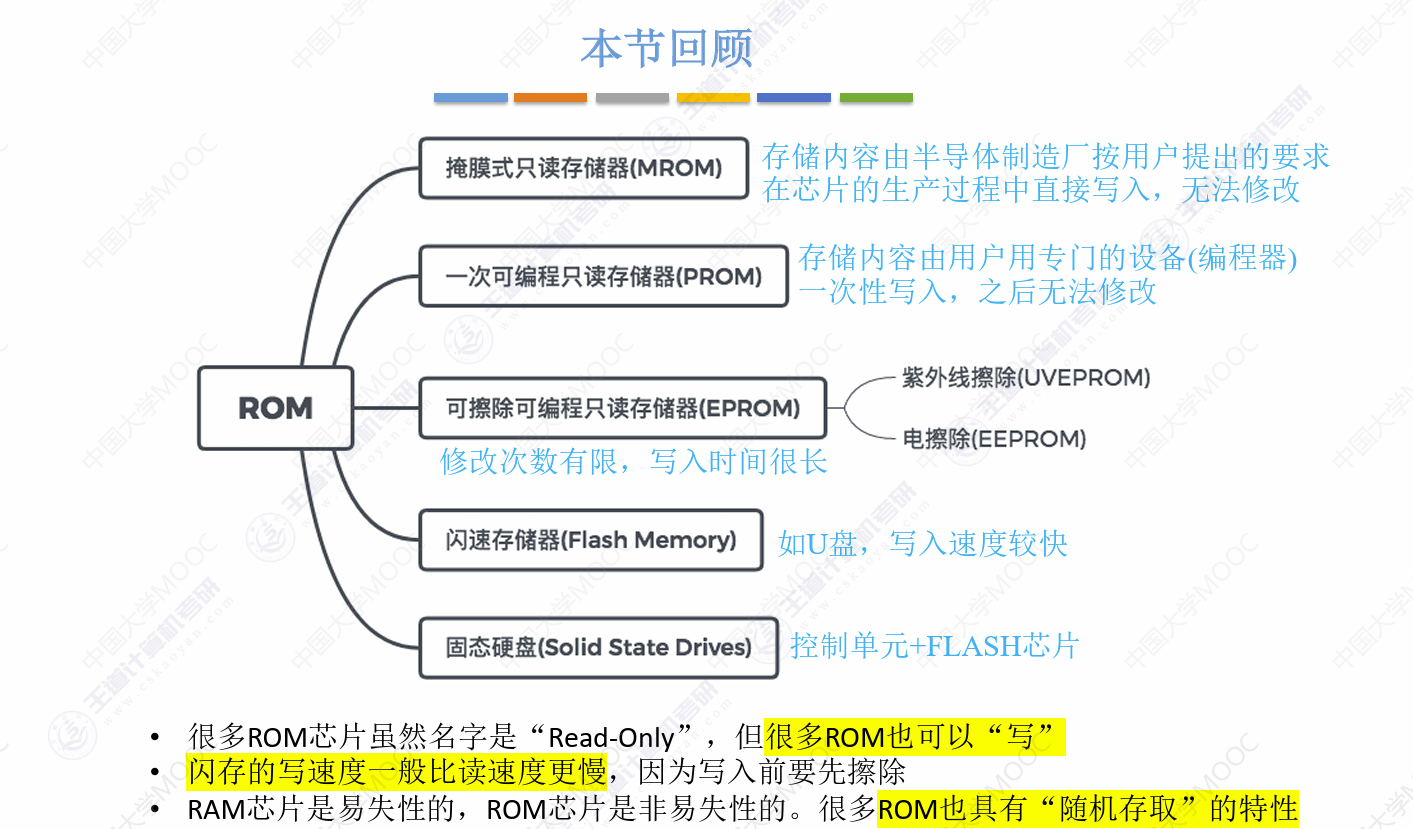

只读存储器:

没太多东西,全都是概念,记住是ROM即可

判断ROM芯片和RAM芯片最本质的特征其实就是看它,到底会不会断电后还保存

另外就是在计组中谈到的主存通常指代ROM(BIOS芯片)+RAM,采用统一编址的方式

多模块存储器:

至于单体,了解即可,需要知道其是总线M个字宽、每个存储单元M个字大、一次取M个字

即每次取一个存储单元(当然其实也就是一行

如果指令、操作数都是连续存放的,那么一次性就能取出来全部的

如果不是连续存放的,不仅每次为了取那么一短段数据需要取一长串出来更浪费

而且还需要访问多行(多个存储单元进行存取,在不连续的情况下更加浪费时间

采用高位交叉编码的,高位是体号,低位是体内地址,体和体之间是顺序的

即体1:0到N-1,体2:N到2N-1…

虽然理论上可以四个存储器一起使用,同时取不同地址的数,但因为CPU大多是顺序存取

所以基本等于只是扩容,而无并行使用,没有拓展吞吐量

采用低位交叉编码的,高位是体内地址,低位是体号,体和体之间的序号要区分

这个因为实现了连续地址存放在不同的存储器,而且CPU大多数是顺序存取

所以基本能完美拓展效率

地址/总体数=体号,通常是四体,同时一般说下,四体默认也就是T=4r(冷却=4存取时间

轮流启动的话,就可以实现完美利用并行的效率,因为一个读完还要冷却

但是如果是顺序读取,顺序的下一位在另外一个存储器,只需要继续读下去即可

不过需要满足一点,就是在第一个存储器已经冷却完了再去读取它

这样就和冷却时间、读取时间联系起来,读取时间乘N=冷却时间,就能让其完美运行

不过如果是一个还在冷却就去读取,那么只能等它冷却完了再读取

另外谈下一块存储器的组成:

一般是由多块存储芯片组成的,存储芯片在逻辑上以矩阵的多维存储为主

因而每次选中一行,实际上是选中了多维的一行,一列,实际上也是多维度的一列

多个存储芯片在逻辑上是重叠起来的

因而就必须有片选线的存在,否则根本不能清楚是选哪个位置

即使是只选那么一行,其实也是多维的一行,一个点,也是多维的一个重叠点

所以行缓冲器存的就是多位面的一行信息,列缓冲器也是同样的,多位面,特指输出时

SDRAM和DRAM的区别就是CPU可以闲着或者CPU不能闲着的区别